台积电5nm打造1700平方毫米巨型中介层

晶体管越来越小,但是高性能计算需求越来越高,有些人就反其道而行之,尝试制造超大芯片。

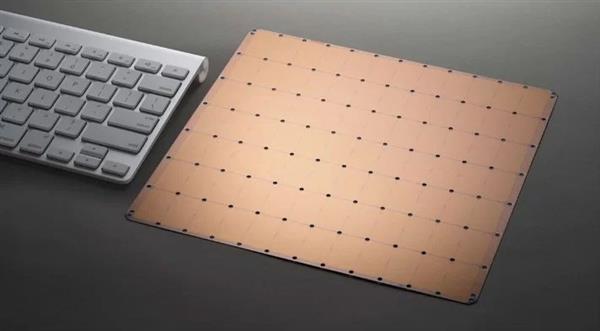

之前我们就见识过Cerebras Systems打造的世界最大芯片WSE,拥有46225平方毫米面积、1.2万亿个晶体管、40万个AI核心、18GB SRAM缓存……并得到了美国能源部的青睐和部署。

现在,台积电、博通联合宣布,双方将利用晶圆上芯片封装(CoWos)技术,打造面积达1700平方毫米的中介层(Interposer),是芯片蚀刻所用光掩模(光罩)尺寸极限858平方毫米的整整两倍。

这样规模的中介层显然是无法一次性单个制造出来的,台积电实际上是同时在晶圆上蚀刻多个中介层,然后将它们连接在一起,组成一个整体。

工艺上,台积电也用上了最先进的5nm EUV(N5),它将在今年上半年投入量产。

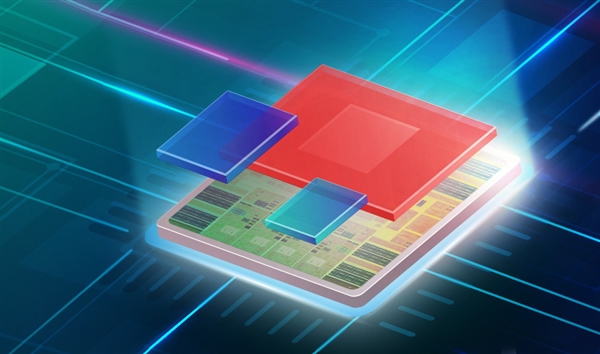

所谓中介层,用途就是串联不同裸片(Die)的桥梁,因为随着现代芯片日益复杂,制造单个大型SoC的代价越来越大,所以行业普遍开发出了各种新的封装技术,将不同的小芯片、模块整合在一起,构成一颗大芯片。

博通就计划用这个庞大无比的中介层,封装多个SoC芯片,以及六颗HMB2内存,单颗容量16GB,总容量达96GB/s,带宽也高达2.7TB/s。

看这规格,应该是三星最新的HBM2E。

台积电和高通未透露这种庞大芯片的具体规格,只是说将用于高性能计算领域。

另外,台积电还在改进CoWoS封装技术,所以未来不排除面积超过1700平方毫米的更大芯片。

关键词:

- 杭州市富阳区:以快递小哥等为代表的新就业形态联合工会已拥有385名实名制会员

- 以创新链赋能产业链!微医与浙大网新签署战略合作协议

- 节水抗旱稻“旱优73”“如何增收”?建德杨村桥镇给出答案

- 梦天实验舱与长征五号B遥四运载火箭组合体进行垂直转运前准备

- 番禺区构建“15分钟文明实践服务圈” 让群众的生活更加丰富多彩

- 无锡古运河IP大放异彩!清名桥历史文化街区五次登上央视

- 苗婉茹夺得女子50米步枪三姿冠军 为中国队拿下一个奥运席位

- 最新消息!《工业过程控制用直行程电动调节阀团队标准》正式颁布

- 全省范围推广!建德“一本账S1”试点医用耗材应用场景上线

- 产城相融为文化地标添新彩!高新区(滨江)点亮文化空间

- 1 优酷视频怎么开弹幕?优酷弹幕怎么没有了?

- 2 怎么查看局域网内所有电脑的信息?怎样加入局域网?

- 3 《笑傲江湖ol》黑屏闪退怎么办?新笑傲江湖闪退如何解决?

- 4 淘宝登陆不上怎么办?手机淘宝进入不了店铺是怎么回事?

- 5 笔记本电脑看视频卡死机怎么办?电脑看视频的时候暂停一段时间后就黑屏死机了是为什么?

- 6 360漏洞修复后蓝屏怎么解决?360更新了补丁以后电脑蓝屏打不开了?

- 7 kindle死机了怎么办?Kindle不提示更新最新固件怎么办?

- 8 windows7如何重装声卡驱动?win7系统电脑声卡驱动在哪里打开?

- 9 泰森智慧工厂日照投产,进一步推行数字化转型

- 10 广东男子不慎刮断电缆线致车辆被扣 京东安联保险快速协助解决获赠锦旗